## DEVICE PERFORMANCE SPECIFICATION

# KODAK KAC-9637 CMOS IMAGE SENSOR

648 (H) X 488 (V) VGA 68 fps Monochrome CIS

September 2004 Revision 1.92

## KAC-9637 Monochrome CMOS Image Sensor VGA 68 FPS

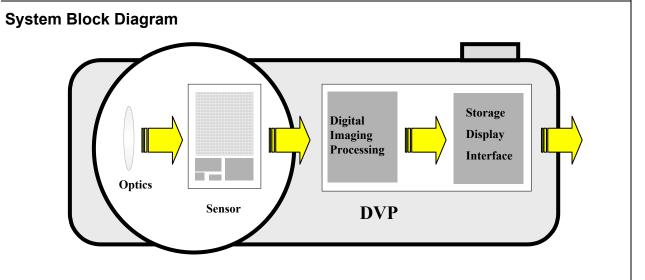

## **General Description**

The KAC-9637 is a high performance, low power, 1/4" VGA CMOS Active Pixel Sensor capable of capturing monochromestill or motion images and converting them to a digital data stream.

Great image quality is achieved by integrating a high performance analog signal processor comprising of a high speed 10 bit A/D convertor, fixed pattern noise elimination circuits and and a programmable gain amplifier. The offset and black level can be automatically adjusted on chip using a full loop black level compensation circuit.

Furthermore, a programmable smart timing and control circuit allowing the user maximum flexibility in adjusting integration time, active window size, gain, frame rate. Various control, timing and power modes are also provided.

## **Features**

- · Master and slave mode operation

- · Progressive scan read out with horizontal and vertical flip

- Programmable Exposure:

- Master clock divider

- Inter row delay

- Inter frame delay

- Partial frame integration

- Programmable gain amplifier

- Full automatic servo loop for black level & offset adjustment on each gain channel

- Horizontal & vertical sub-sampling (2:1 & 4:2)

- Windowing

- · Programmable pixel clock, inter-frame and inter-line delays

- I<sup>2</sup>C compatible serial control interface

- · Power on reset & power down mode

## **Applications**

- Dual Mode Camera

- Digital Still Camera

- Security Camera

- Machine Vision

## **Key Specifications**

| Array Format         | Total: 488 x 672<br>Active: 488(V) x 648(H)       |

|----------------------|---------------------------------------------------|

| Effective Image Area | Total: 2.93mm x 4.03mm<br>Active: 2.93mm x 3.89mm |

| Optical Format       | 1/4"                                              |

| Pixel Size           | 6.0μm x 6.0μm                                     |

| Video Outputs        | 8 & 10 Bit Digital                                |

| Frame Rate           | 68 frames per second                              |

| Dynamic Range        | 57 dB                                             |

| Electronic Shutter   | Rolling Reset                                     |

| FPN                  | 0.2%                                              |

| PRNU                 | 1.7%                                              |

| Sensitivity          | 2.40 volts/lux*s                                  |

| Fill Factor          | 49%                                               |

| Micro Lens           | none                                              |

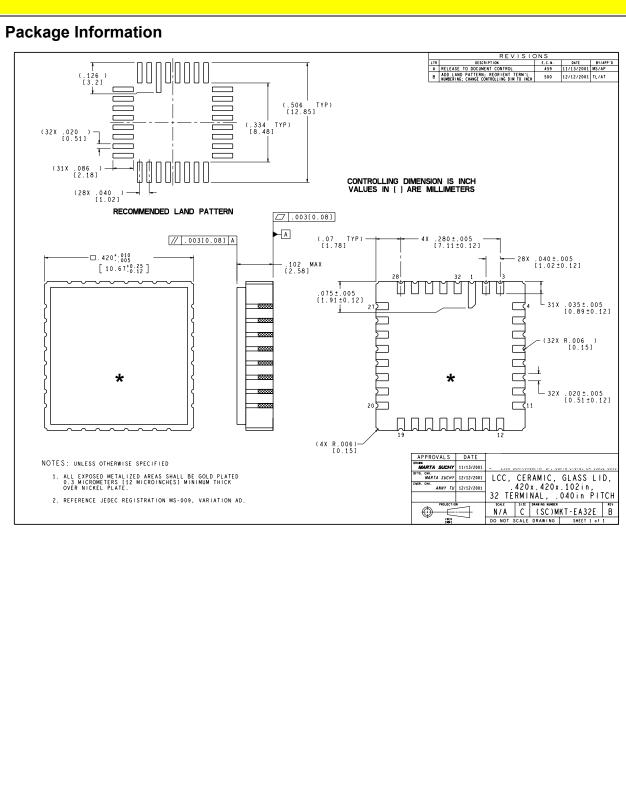

| Package              | 32 LCC                                            |

| Single Supply        | 3.0V +/-10%                                       |

| Power Consumption    | 130mW                                             |

| Operating Temp       | -10°C to 50°C                                     |

#### Email:imagers@kodak.com

# **Kodak**

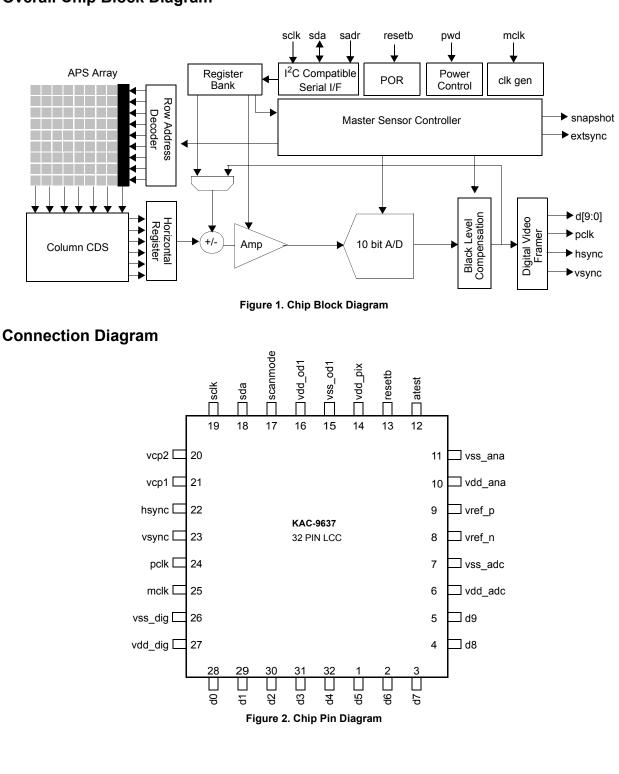

## **Overall Chip Block Diagram**

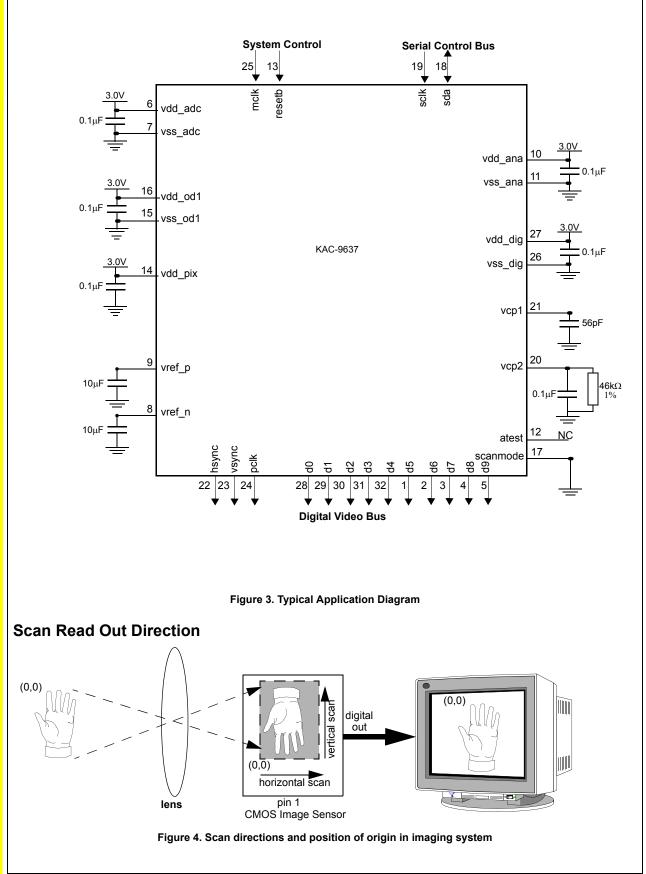

## **Typical Application Circuit**

## Pin Descriptions

KAC-9637

| Pin | Name     | I/O | Тур | Description                                                                                                                                                                                                                                                                                                                  |  |

|-----|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | d5       | 0   | D   | Digital output. Bit 5 of the digital video output bus. This output can be tri-stated                                                                                                                                                                                                                                         |  |

| 2   | d6       | 0   | D   | Digital output. Bit 6 of the digital video output bus. This output can be tri-stated                                                                                                                                                                                                                                         |  |

| 3   | d7       | 0   | D   | Digital output. Bit 7 of the digital video output bus. This output can be tri-stated                                                                                                                                                                                                                                         |  |

| 4   | d8       | 0   | D   | Digital output. Bit 8 of the digital video output bus. This output can be tri-stated                                                                                                                                                                                                                                         |  |

| 5   | d9       | 0   | D   | Digital output. Bit 9 of the digital video output bus. This output can be tri-stated                                                                                                                                                                                                                                         |  |

| 6   | vdd_adc  | I   | Р   | 3.0 volt supply for the 10 bit A/D converter.                                                                                                                                                                                                                                                                                |  |

| 7   | vss_adc  | I   | Р   | 0 volt supply for the 10 bit A/D converter.                                                                                                                                                                                                                                                                                  |  |

| 8   | vref_n   | I   | A   | A/D reference resistor ladder low voltage. This is the bottom of the ADC reference ladder and is normally bypassed with a 10 $\mu F$ capacitor.                                                                                                                                                                              |  |

| 9   | vref_p   | I   | A   | A/D reference resistor ladder high voltage. This is the top of the ADC reference ladd and is normally bypassed with a 10 $\mu F$ capacitor.                                                                                                                                                                                  |  |

| 10  | vdd_ana  | I   | Р   | 3.0 volt supply for analog circuits.                                                                                                                                                                                                                                                                                         |  |

| 11  | vss_ana  | I   | Р   | 0 volt supply for analog circuits.                                                                                                                                                                                                                                                                                           |  |

| 12  | atest    | 0   | А   | Analog test pin. This pin is used for production testing and should not be connected.                                                                                                                                                                                                                                        |  |

| 13  | resetb   | I   | D   | Digital input with pull up resistor. When forced to a logic 0 the sensor is reset to its defau power up state.                                                                                                                                                                                                               |  |

| 14  | vdd_pix  | I   | Р   | 3.0 volt supply for the pixel array. This pin should be connected to the 3.0v analog supp<br>and bypassed to ground with a 10uF capacitor.                                                                                                                                                                                   |  |

| 15  | vss_od1  | I   | Р   | 0 volt supply for the digital IO buffers                                                                                                                                                                                                                                                                                     |  |

| 16  | vdd_od1  | I   | Р   | 3.0 volt supply for the digital IO buffers.                                                                                                                                                                                                                                                                                  |  |

| 17  | scanmode | I   | D   | Digital production test pin. This pin should be tied to ground                                                                                                                                                                                                                                                               |  |

| 18  | sda      | Ю   | D   | I <sup>2</sup> C compatible serial interface data bus.                                                                                                                                                                                                                                                                       |  |

| 19  | sclk     | I   | D   | I <sup>2</sup> C compatible serial interface clock.                                                                                                                                                                                                                                                                          |  |

| 20  | vcp2     | 0   | A   | Analog output, reset charge pump 2 output, connect to vss_ana via a $0.1\mu f$ capacitor. Voltage on this pin should be 5 volt.                                                                                                                                                                                              |  |

| 21  | vcp1     | 0   | A   | Analog output, reset charge pump 1 output, connect to vss_ana via a 56pf capacitor.<br>Voltage on this pin should be 3.6 volt.                                                                                                                                                                                               |  |

| 22  | hsync    | Ю   | D   | Digital Bidirectional. This is a dual mode pin. When the sensor's digital video port is co figured to be a master, this pin is an output and is the horizontal synchronization pulse When the sensor's digital video port is configured to be a slave, (the default), this pin is an input and is the row trigger.           |  |

| 23  | vsync    | IO  | D   | Digital Bidirectional. This is a dual mode pin. When the sensor's digital video port is co<br>figured to be a master, this pin is an output and is the vertical synchronization pulse.<br>When the sensor's digital video port is configured to be a slave, (the default), this pin is<br>an input and is the frame trigger. |  |

KAC-9637

| Ρ | in Descriptions (continued)                                 |                                                                       |                                                                                           |   |                                                                                      |  |  |  |

|---|-------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------|--|--|--|

|   | Pin Name I/O Typ Description                                |                                                                       |                                                                                           |   | Description                                                                          |  |  |  |

|   | 24 pclk O D Digital output. The pixel clock.                |                                                                       | Digital output. The pixel clock.                                                          |   |                                                                                      |  |  |  |

|   | 25 mclk I D Digital input. The sensor's master clock input. |                                                                       |                                                                                           |   |                                                                                      |  |  |  |

|   | 26                                                          | vss_dig     I     P     0 volt power supply for the digital circuits. |                                                                                           |   |                                                                                      |  |  |  |

|   | 27                                                          | vdd_dig                                                               | I                                                                                         | Р | 3.0 volt power supply for the digital circuits.                                      |  |  |  |

|   | 29                                                          | d1                                                                    | O D Digital output. Bit 1 of the digital video output bus. This output can be tri-stated. |   |                                                                                      |  |  |  |

|   | 30                                                          | d2                                                                    | 0                                                                                         | D | Digital output. Bit 2 of the digital video output bus. This output can be tri-stated |  |  |  |

|   | 31                                                          | d3                                                                    | O D Digital output. Bit 3 of the digital video output bus. This output can be tri-stated  |   |                                                                                      |  |  |  |

|   | 32                                                          | d4                                                                    | 0                                                                                         | D | Digital output. Bit 4 of the digital video output bus. This output can be tri-stated |  |  |  |

Legend: (I=Input), (O=Output), (IO=Bi-directional), (P=Power), (D=Digital), (A=Analog).

## Absolute Maximum Ratings (Notes 1 & 2)

| Any Positive Supply Voltage                | 4.2V           |

|--------------------------------------------|----------------|

| Voltage On Any Input or Output Pin         | -0.3V to 4.2V  |

| Input Current at any pin (Note 3)          | ±35mA          |

| Package Input Current (Note 3              | ±50mA          |

| Package Dissipation at $T_A = 25^{\circ}C$ | see Note 4     |

| ESD Susceptibility (Note 5)                |                |

| Human Body Model                           | 2000V          |

| Machine Model                              | 200V           |

| Peak Soldering Temperature (Note 6)        | 235°C          |

| Storage Temperature                        | -40°C to 125°C |

|                                            |                |

## Operating Ratings (Notes 1 & 2)

Operating Temperature Range All VDD Supply Voltages

-10°C≤T≤+50°C +2.7V to +3.3V

## DC and logic level specifications

| Symbol            | Parameter                         | Conditions                          | Min<br>note 9    | Typical<br>note 8 | Max<br>note 9 | Unit           |

|-------------------|-----------------------------------|-------------------------------------|------------------|-------------------|---------------|----------------|

| scik, sda i       | Digital Input/Output Characterist | lics                                |                  |                   |               |                |

| VIH               | Logical "1" Input Voltage         |                                     | 0.7*vdd_od       |                   | vdd_od+0.5    | V              |

| VIL               | Logical "0" Input Voltage         |                                     | -0.5             |                   | 0.3*vdd_od    | V              |

| VOL               | Logical "0" Output Voltage        | vdd_od = +2.7V, lout=3.0mA          |                  |                   | 0.4           | V              |

| V <sub>hys</sub>  | Hysteresis (SCLK pin only)        | vdd_od > +2.0V                      | 0.05*vdd_od      |                   |               | V              |

| I <sub>leak</sub> | Input Leakage Current             | Vin=vdd_od                          |                  | 1                 |               | μA             |

| nclk, rese        | etb, hsync, vsync Digital Input C | haracteristics                      |                  |                   |               | 1              |

| VIH               | Logical "1" Input Voltage         | vdd_dig = +3.3V                     | 2.0              |                   |               | V              |

| VIL               | Logical "0" Input Voltage         | vdd_dig = +2.7V                     |                  |                   | 0.8           | V              |

| IIH               | Logical "1" Input Current         | VIH = vdd_dig                       |                  | 1                 |               | nA             |

| IIL               | Logical "0" Input Current         | VIL = vss_dig                       |                  | -1                |               | nA             |

| d0 - d9, po       | clk, hsync, vsync Digital Output  | Characteristics                     |                  |                   |               | <u> </u>       |

| VOH               | Logical "1" Output Voltage        | vdd_od=2.7V, lout=-1.6mA            | 2.2              |                   |               | V              |

| VOL               | Logical "0" Output Voltage        | vdd_od=2.7V, lout =-1.6mA           |                  |                   | 0.5           | V              |

| IOZ               | TRI-STATE Output Current          | VOUT = vss_od<br>VOUT = vdd_od      |                  | -0.1<br>0.1       |               | μA<br>μA       |

| IOS               | Output Short Circuit Current      |                                     |                  | +/-17             |               | mA             |

| Power Su          | pply Characteristics              |                                     |                  |                   |               |                |

| IA                | Analog Supply Current             | Power down mode<br>Operational mode | @27MHz<br>@12MHz | 670<br>60<br>50   |               | μA<br>mA<br>mA |

| ID                | Digital Supply Current            | Power down mode<br>Operational mode | @27MHz<br>@12MHz | 0<br>28<br>13     |               | μA<br>mA<br>mA |

## **Power Dissipation Specifications**

| The following specifications apply for all VDD pins= +3.0V. Boldfa | ce limits apply for TA = $T_{MIN}$ to $T_{MAX}$ : all other limits $T_A = 25^{\circ}C$ . |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Symbol           | Parameter                 | Conditions        | Min<br>note 9 | Typical<br>note 8 | Max<br>note 9 | Units    |

|------------------|---------------------------|-------------------|---------------|-------------------|---------------|----------|

| P <sub>dwn</sub> | Power Down                |                   |               | 2.0               |               | mW       |

| PWR              | Average Power Dissipation | @27 MHz<br>@12MHz |               | 264<br>189        |               | mW<br>mW |

|               | • •                                   |                                        |                         |                           |                 |          |

|---------------|---------------------------------------|----------------------------------------|-------------------------|---------------------------|-----------------|----------|

| The following | specifications apply for all VDD pins | s= +3.0V. Boldface limits apply for TA | A = T <sub>MIN</sub> to | T <sub>MAX</sub> : all of | her limits T    | A = 25°C |

| Symbol        | Parameter                             | Conditions                             | Min<br>(note 9)         | Typical<br>(note 8)       | Max<br>(note 9) | Units    |

|               |                                       |                                        |                         |                           |                 |          |

| Oymbol | i arameter      | Conditions          | (note 9) | (note 8) | (note 9) |      |

|--------|-----------------|---------------------|----------|----------|----------|------|

|        | Gain Resolution |                     |          | 7        |          | Bits |

|        | Step Size       | (Gain / Resolution) |          | 0.125    |          | dB   |

|        | Maximum Gain    |                     |          | 16       |          | dB   |

|        | Minimum Gain    |                     |          | 0.0      |          | dB   |

## AC Electrical Characteristics

Video Amplifier Specifications

| Symbol                            | Parameter                            | Conditions           | Min<br>note 9 | Typical<br>note 8 | Max<br>note 9 | Units   |

|-----------------------------------|--------------------------------------|----------------------|---------------|-------------------|---------------|---------|

| F <sub>mclk</sub>                 | Input Clock Frequency                |                      | 12            |                   | 27            | MHz     |

| T <sub>ch</sub>                   | Clock High Time                      | @ CLK <sub>max</sub> | 16.0          |                   |               | ns      |

| T <sub>cl</sub>                   | Clock Low Time                       | @ CLK <sub>max</sub> | 16.0          |                   |               | ns      |

|                                   | Clock Duty Cycle                     | @ CLK <sub>max</sub> | 45/55         | 50/50             | 55/45         | min/max |

| T <sub>rc</sub> , T <sub>fc</sub> | Clock Input Rise and Fall Time       |                      |               | 3                 |               | ns      |

| F <sub>hclk</sub>                 | Internal System Clock Fre-<br>quency |                      | 12            |                   | 27            | MHz     |

| T <sub>reset</sub>                | Reset pulse width                    |                      | 1.0           |                   |               | μS      |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

All voltages are measured with respect to vss dig = vss ana = vss adc = vss od1 = vss od2 = 0V, unless otherwise Note 2: specified.

Note 3: When the voltage at any pin exceeds the power supplies (VIN < [vss\_dig or vss\_ana or vss\_adc or vss\_od1 or vss\_od2] or VIN > [vdd\_dig or vdd\_ana or vdd\_adc or vdd\_od1 or vdd\_od2]), the current at that pin should be limited to 25mA. The 50mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25mA to two.

The absolute maximum junction temperature (TJmax) for this device is 150°C. The maximum allowable power dissipation Note 4 is dictated by TJmax, the junction-to-ambient thermal resistance ( $\Theta_{JA}$ ), and the ambient temperature (TA), and can be cal-

culated using the formula PDMAX = (TJmax - TA)/ $\Theta_{JA}$ . In the 48-pin LCC,  $\Theta_{JA}$  is 69°C/W, so PDMAX = 1,811mW at 25°C

and 1,449 mW at the maximum operating ambient temperature of 50°C. Note that the power dissipation of this device under normal operation will typically be about 215 mW. The values for maximum power dissipation listed above will be reached only when the KAC-9637 is operated in a severe fault condition.

Note 5: Human body model is 100pF capacitor discharged through a 1.5kΩ resistor. Machine model is 220pF discharged through **ZERO Ohms**

See AN450, "Surface Mounting Methods and Their Effect on Product Reliability", or the section entitled "Surface Mount" Note 6: found in any post 1986 National Semiconductor Linear Data Book, for other methods of soldering surface mount devices. Note 7: The analog inputs are protected as shown below. Input voltage magnitude up to 500mV beyond the supply rails will not

damage this device. However, input errors will be generated If the input goes above AV+ and below AGND.

Typical figures are at TJ = 25°C, and represent most likely parametric norms Note 8:

Note 9: Test limits are guaranteed to AOQL (Average Outgoing Quality Level).

| Parameter                                         | Value                      | Units            |

|---------------------------------------------------|----------------------------|------------------|

| Number of pixels (row, column)<br>Total<br>Active | 488 x 672<br>488 x 648     | pixels<br>pixels |

| Array size (x,y Dimensions)<br>Total<br>Active    | 2.93 x 4.03<br>2.93 x 3.89 | mm<br>mm         |

| Pixel Pitch                                       | 6.0                        | μ                |

| Fill Factor without micro-lens                    | 49                         | %                |

## **Image Sensor Specifications**

The following specifications apply for All VDD pins = +3.3V,  $T_A = 25^{\circ}$ C, Illumination Color Temperature = 2850°K, IR cutoff filter at 700nm, **mclk** = 27MHz, frame rate = 15Hz, unity video gain.

| Parameter                                                                                                                                   | neter Description                                                                                            |  | Typical<br>note 8 | Max<br>note 9 | Units      |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|-------------------|---------------|------------|

| Optical Sensitivity <sup>1</sup>                                                                                                            | Measured at the input of the A/D                                                                             |  | 2.40              |               | Volt/lux.s |

| Dark Signal                                                                                                                                 | The pixel output signal due to dark cur-<br>rent.                                                            |  | 0.15              |               | Volt/s     |

| Read Noise                                                                                                                                  | The RMS temporal noise of the pixel out-<br>put signal in the dark averaged over all<br>pixels in the array. |  | 1.5               |               | LSBs       |

| Dynamic Range The ratio of the saturation pixel output signal and the read noise expressed in dB.                                           |                                                                                                              |  | 57                |               | dB         |

| FPN                                                                                                                                         | Fixed Pattern Noise: the RMS spatial noise in the dark excluding the effect of read noise.                   |  | 0.2               |               | %          |

| PRNU Photo Response Non Uniformity: the<br>RMS variation of pixel sensitivities as a<br>percentage of the average optical sensi-<br>tivity. |                                                                                                              |  | 1.5               |               | %          |

1 The optical sensitivity at the A/D output, in units of LSBs/lux.s, can be calculated using:  $\frac{1024}{vrefp-vrefn}$  · Optical Sensitivity

KAC-9637

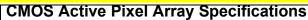

Figure 5. Spectral Response Curve

## **Functional Description**

## 1.0 OVERVIEW

KAC-9637

## 1.1 Light Capture and Conversion

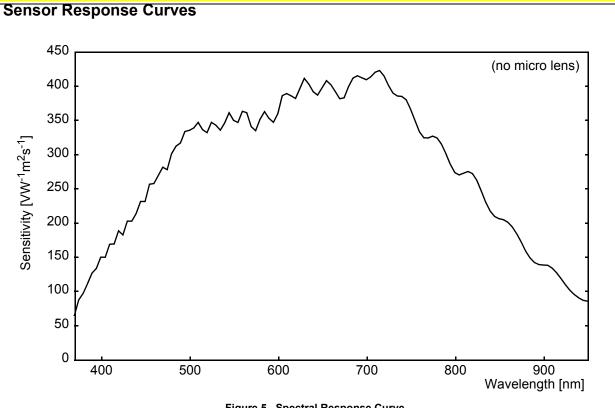

The KAC-9637 contains a CMOS active pixel array consisting of 488 rows by 648 columns. 24 columns of optically shielded (black) pixels are provided to the right of the array as shown in Figure 6. Only the middle 8 black columns are used for black level compensation. The black pixels are physically located at the end of each row but are read out first.

Figure 6. CMOS APS region of the KAC-9637

At the beginning of a given integration time the on-board timing and control circuit will reset every pixel in the array one row at a time as shown in Figure 7. Note that all pixels in the same row are simultaneously reset, but not all pixels in the array.

Figure 7. CMOS APS Row and Column addressing scheme

At the end of the integration time, the timing and control circuit will address each row and simultaneously transfer the integrated value of the pixel to a correlated double sampling circuit and then to a shift register as shown in Figure 7.

Once the correlated double sampled signals have been loaded into the shift register, the timing and control circuit will shift them out one pixel at a time.

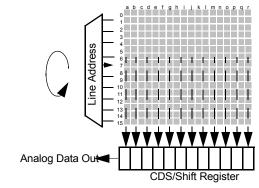

The analog pixel signal is then fed into an analog gain channel as shown in figure 8. The gain channel can be digitally programmed allowing the signal level of pixel to be adjusted.

After gain adjustment the analog value of each pixel is converted to a 10 bit digital data as shown in figure 8.

Figure 8. Analog Signal Conditioning & Conversion to Digital

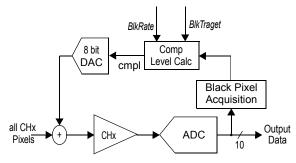

The black level together with the full analog signal path offset is automatically compensated as shown in figure 8. This can be manually overridden.

Figure 9. Digital Pixel Processing.

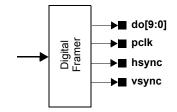

Finally the pixel data is framed and output on the digital video bus as shown in figure 9.

## 1.2 Program and Control Interfaces

The programming, control and status monitoring of the KAC-9637 is achieved through a two wire  $I^2C$  compatible serial bus. A device address pin is provided allowing two different device addresses to be selected for the serial interface as shown in Figure 10.

Figure 10. Control Interface to the KAC-9637.

## Functional Description (continued)

## 2.0 DOUBLE BUFFERED REGISTERS

All programmable registers that effect the frame rate and integration timing are double buffered; such that the new values only take effect at the start of the new frame. When writing to all split double buffered registers, e.g. ITIMEH and ITIMEL, the following procedure must be followed:

- to change both the MSB and LSB, first write to the MSB register and then write to the LSB register,

- to change only the MSB, first write to the MSB register and then write the unchanged value of the LSB to the LSB register,

- to only change the LSB write to the LSB register.

## 3.0 WINDOWING

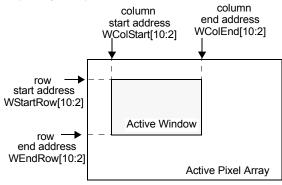

The integrated timing and control circuit allows any size window in any position within the active region of the array to be read out with a 4x4 pixel resolution. The window read out is called the *"Active Window"*.

Four coordinates (start row address, start column address, end row address & end column address) need to be programmed to define the size and location of the "*Active Window*" to be read out (*see Figure 11*).

## Figure 11. Windowing

## Notes:

By default the "Active Window" is set to 320 columns by 240 rows. To program a VGA window aligned to the optical center to the pixel array the following codes need to be written to the windowing registers via the I<sup>2</sup>C interface

| W | windowing registers via the I-C interface |         |     |  |  |  |

|---|-------------------------------------------|---------|-----|--|--|--|

|   | 19h                                       | WROWS   | 00h |  |  |  |

|   | 1Ah                                       | WROWE   | 3Bh |  |  |  |

|   | 1Bh                                       | WROWLSB | 23h |  |  |  |

|   | 1Ch                                       | WCOLS   | 00h |  |  |  |

|   | 1Dh                                       | WCOLE   | 50h |  |  |  |

|   | 1Eh                                       | WCOLLSB | 23h |  |  |  |

• The "Active Window" registers are double buffered.

• The black pixels are read out at the beginning of each row even when not contained in the active window. The black pixel read out can be masked by setting the *BIKPixelEn* bit in the DVBUSCONFIG2 register to a logic 0.

## 4.0 ARRAY READOUT

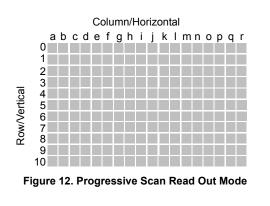

The pixels in the array are read out in progressive scan. In progressive scan, every pixel in every row in the defined *"Active Window"* is consecutively read out, one pixel at a time. The first 8 pixels of every row are black unless masked out by setting the *BlkPixelEn* bit of the DVBUSCONFIG2 register to a logic 0.

The scan direction can be programmed as follows:

| Scan Direction                                      | VScanDir | HScanDir |

|-----------------------------------------------------|----------|----------|

| Default Scan Direction                              | 1        | 1        |

| Reverse Vertical Scan<br>Direction                  | 0        | 1        |

| Reverse Horizontal Scan<br>Direction                | 1        | 0        |

| Reverse Vertical and Hori-<br>zontal Scan Direction | 0        | 0        |

#### 4.1 Default Scan Direction

The default scan direction is to consecutively read out, one pixel at a time, starting with the left most pixel in the top most row. Hence, for the example shown in Figure 12, the read out order will be a0,b0,...,r0 then a1,b1,...,r1 and so on until pixel r20 is read out. See figure 12.

#### 4.2 Reverse Vertical Scan Direction

The vertical scan direction can be reversed by setting the "VScanDir" bit in the VSCAN register to a logic 0, while setting the HScanDir bit in the HSCAN register to a logic 1. In this case for the example shown in Figure 12, the read out order will be *a10,b10,...,r10* then *a9,b9,...,r9* and so on until pixel *r0* is read out.

#### 4.3 Reverse Horizontal Scan Direction

The horizontal scan direction can be reversed by setting the "HScanDir" bit in the HSCAN register to a logic 0, while setting the "VScanDir" bit in the VSCAN register to a logic 1. In this case for the example shown in Figure 12, the read out order will be r0,q0,...,a0 then r1,q1,...,a1 and so on until pixel a10 is read out.

#### 4.4 Reversing The Horizontal & Vertical Scan Direction

The horizontal scan direction can be reversed by setting both the "HScanDir" bit in the HSCAN and the "VScanDir" bit in the VSCAN register to a logic 0. In this case for the example shown in Figure 12, the read out order will be r10,q10,...,a10 then r9,q9,...,a9 and so on until pixel a0 is read out.

## Functional Description (continued)

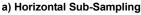

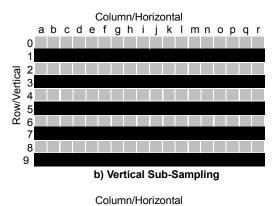

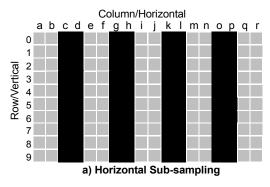

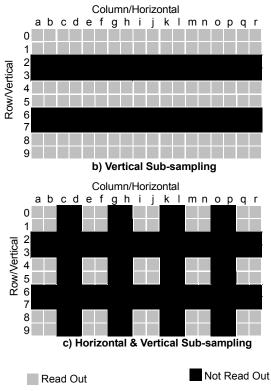

#### SUB-SAMPLING MODES 5.0

#### 5.1 2:1 Sub-Sampling

KAC-9637

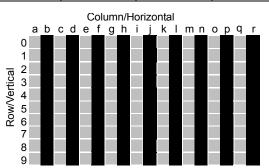

The timing and control circuit can be programmed to sub-sample pixels in the "Active Window" vertically, horizontally or both, with an aspect ratio of 2:1 as illustrated in figure 13.

| Register<br>Bit | VIDCONFIG<br>Color | VSCAN<br>VSub | HSCAN<br>HSub |

|-----------------|--------------------|---------------|---------------|

| Vertical        | 0                  | 1             | 0             |

| Horizontal      | 0                  | 0             | 1             |

| Both            | 0                  | 1             | 1             |

Read Out

#### Figure 13. Example of 2:1 Sub-sampling

- Note that the pixel read out will depend on the pro-Note a: grammed scan order as described in section 4.0.

- Note b: For max FPN performance it is recommended to always switch on the averaging feature when subsampling (see next section).

#### 5.2 2:1 Sub-Sampling with Averaging

The timing and control circuit can be programmed to average neighboring pixels in the analog domain before sub-sampling in the horizontal direction only as shown in the table below

| Register   | VIDCONFIG | VSCAN | HSCAN |

|------------|-----------|-------|-------|

| Bit        | Color     | VAvr  | HAvr  |

| Horizontal | 0         | 0     | 1     |

When horizontal 2:1 subsampling with averaging is selected, neighboring pixels in the horizontal direction are combined as shown in figure 14. The value of the combined pixel is given by

| - | а              | b              | с              | d              | е              | f              | g              | h              | i              | j              |

|---|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1 | $H_1$          | H <sub>2</sub> | H <sub>1</sub> | $H_2$          | H <sub>1</sub> | H <sub>2</sub> | H <sub>1</sub> | H <sub>2</sub> | H <sub>1</sub> | H <sub>2</sub> |

| - | H <sub>1</sub> | $H_2$          | H <sub>1</sub> | $H_2$          | $H_1$          | H <sub>2</sub> | H <sub>1</sub> | H <sub>2</sub> | H <sub>1</sub> | H <sub>2</sub> |

| 2 | H <sub>1</sub> | H <sub>2</sub> |

|   | H <sub>1</sub> | H <sub>2</sub> |

## Functional Description (continued)

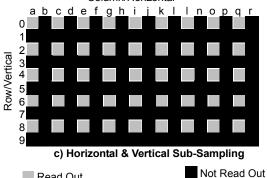

#### 5.3 4:2 Sub-Sampling

The timing and control circuit can be programmed to sub-sample pixels in the display window vertically, horizontally or both, with an aspect ratio of 4:2 as illustrated in figure 15

| Register<br>Bit | VIDCONFIG<br>Color | VSCAN<br>VSub | HSCAN<br>HSub |

|-----------------|--------------------|---------------|---------------|

| Vertical        | 1                  | 1             | 0             |

| Horizontal      | 1                  | 0             | 1             |

| Both            | 1                  | 1             | 1             |

#### Figure 15. Example 4:2 Sub-sampling

Note a: Note that the pixel read out will depend on the programmed scan order as described in section 4.0. Note b: For max FPN performance it is recommended to always switch on the averaging feature when subsampling (see next section).

#### 5.4 4:2 Sub-Sampling with Averaging

The timing and control circuit can be programmed to average neighboring pixels of the same color in the analog domain before subsampling. This can be done in the horizontal direction only as shown in the table below:

| Register   | VIDCONFIG | VSCAN | HSCAN |

|------------|-----------|-------|-------|

| Bit        | Color     | VAvr  | HAvr  |

| Horizontal | 1         | 0     | 1     |

When **horizontal** 2:1 subsampling with averaging is selected, neighboring pixels in the horizontal direction are combined as shown in figure 16. The value of the combined pixel is given by

|   | а              | b              | с              | d              | е              | f       | g              | h              |

|---|----------------|----------------|----------------|----------------|----------------|---------|----------------|----------------|

| 1 | H <sub>1</sub> | $\mathbb{H}_1$ | $H_2$          | H <sub>2</sub> | H <sub>1</sub> | $H_1$   | H <sub>2</sub> | H <sub>2</sub> |

|   | H <sub>1</sub> | $\mathbb{H}_1$ | H <sub>2</sub> | H <sub>2</sub> | H <sub>1</sub> | $(H_1)$ | H <sub>2</sub> | H <sub>2</sub> |

|   |                |                |                | H <sub>2</sub> |                |         |                |                |

|   | H <sub>1</sub> | $(H_1)$        | H <sub>2</sub> | H <sub>2</sub> | H <sub>1</sub> | $(H_1)$ | H <sub>2</sub> | H <sub>2</sub> |

Figure 16. :4:2Horizontal Subsampling with Averaging

## Functional Description (continued)

## 6.0 FRAME RATE & EXPOSURE CONTROL

#### 6.1 Introduction

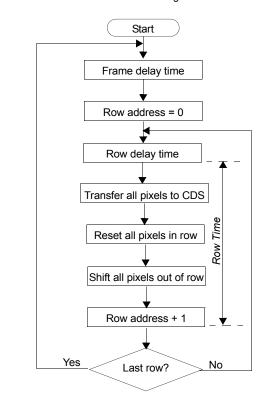

The frame time is defined as the time it takes to reset every pixel in the array, integrate the incident light, convert it to digital data and present it on the digital video port. This is not a concurrent process and is characterized in a series of events each requiring a certain amount of time as shown in Figure 17.

#### Figure 17. Frame Readout Flow Diagram

The following factors effect frame rate, exposure & signal level, the:

- frequency of Hclk

- size of the "Active Window"

- subsampling mode

- · programmed row delay

- programmed frame delay.

The following factor effects signal level only.

· analog gain

The following factor effects exposure & signal level:

integration time

This section describes how to program the frame rate and exposure time.

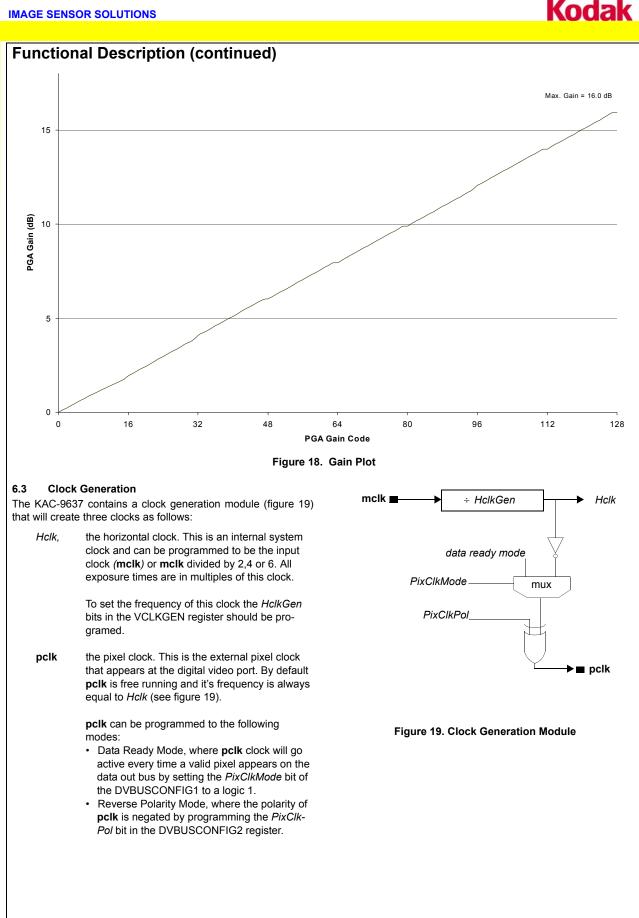

#### 6.2 Analog Gain

A programmable analog gain amplifier is provided, allowing the gain level of the in-comming pixels to be adjusted before the analog to digital conversion.

16dB of gain programmable in 128 steps of 0.125dB, (see the PGA register). Note: Set register 0x4Ah to 0x00h when using monochrome mode

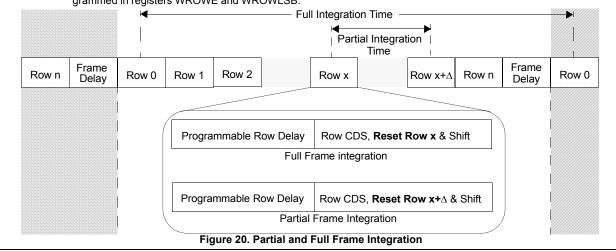

## 6.4 Full Frame Integration

Full frame integration is when each pixel in the array integrates light incident on it for the duration of a frame (see Figure 20).

The number of pixels processed per row is given by:

Functional Description (continued)

Where:

WEndCol is the "Active Window" column start address as programmed in registers WCOLE and WCOL-LSB.

WStartCol

is the "Active Window" column end address as programmed in registers WCOLS and WCOL-LSB.

The number of *Hclk* clock cycles required to process & shift out one row of pixels is given by:

#### $RN_{HClk} = R_{opcycle} + R_{ltime} + (N_{pix}*MH_{factor}) + R_{delay}$

Where:

| R <sub>opcycle</sub> | is a fixed integer value of 137 representing the                                                              |

|----------------------|---------------------------------------------------------------------------------------------------------------|

| , ,                  | Row Operation Cycle Time in multiples of Hclk                                                                 |

|                      | clock cycles. It is the time required to carry out                                                            |

|                      | all fixed row operations outlined in Figure 17.                                                               |

| R <sub>Itime</sub>   | When partial frame integration is enabled, (Prt-                                                              |

|                      | <i>FrmEn</i> bit in the ITIMECONFIG register is set to a logic 1), $R_{ltime}$ is a fixed integer of 37. When |

|                      | Partial frame integration is disabled, ( <i>PrtFrmEn</i>                                                      |

|                      | bit in the ITIMECONFIG register is set to a logic                                                             |

|                      | 0), <i>R<sub>Itime</sub></i> is a fixed integer of 0.                                                         |

| N <sub>pix</sub>     | Is the number of pixels processed in a row.                                                                   |

| MH <sub>factor</sub> | Is 1 when horizontal subsampling is disabled                                                                  |

|                      | and 0.5 when horizontal subsampling is<br>enabled.                                                            |

| R <sub>delav</sub>   | a programmable value between 0 & 8191 repre-                                                                  |

| uciay                | senting the Row Delay Time in multiples of <i>Hclk</i> .                                                      |

|                      | This parameter allows the Row Operation Cycle                                                                 |

|                      | time to be extended. The Rdelay value is pro-                                                                 |

|                      | grammed in the RDELAYH and RDELAYL registers.                                                                 |

|                      |                                                                                                               |

The number of rows in the active window is given by: *N*<sub>rows</sub> = (*WEndRow - WStartRow + 1*) \* *MV*<sub>factor</sub>

Where:

WEndRow

is the "Active Window" row start address as programmed in registers WROWE and WROWLSB. WStartRow

is the "Active Window" row end address as programmed in registers WROWS and WROWLSB.

MV<sub>factor</sub>

is 1 when vertical subsampling is disabled and

0.5 when vertical subsampling is enabled. The number of *Hclk* clocks required to process a full frame is given by:

Where:

N<sub>rows</sub> F<sub>delay</sub> is the number of rows in the "Active Window".

a programmable value between 0 & 32766 representing the *Inter Frame Delay* in multiples of  $RN_{Hclk}$ . This parameter allows the frame time to be extended. (See the Frame Delay High and Frame Delay Low registers). The *Fdelay* value is programmed in the FDELAYH and FDELAYL registers.

The frame rate is given by:

#### 6.5 Partial Frame Integration

In some cases it is desirable to reduce the time during which the pixels in the array are allowed to integrate incident light without changing the frame rate.

This is known as *Partial Frame Integration* and can be achieved by resetting pixels in a given row ahead of the row being selected for readout as shown in Figure 20. The number of *Hclk* clocks required to process a partial frame is given by:

#### FP<sub>Hclk</sub> = RN<sub>Hclk</sub> \* Itime

Where:

| RN <sub>Hclk</sub> | is the number of Hclk clock cycles required to                                                                                                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Itime              | process & shift out one row of pixels.<br>a programmable value between 0 & 32767 rep-                                                                     |

|                    | resenting the number of rows ahead of the cur-<br>rent row to be reset. This value must not be<br>larger than the number of active rows. The <i>Itime</i> |

|                    | value is programmed in the ITIMEH and ITIMEL registers.                                                                                                   |

| ata                |                                                                                                                                                           |

Note:

Upon system reset the partial frame integration is automatically enabled. It can be disabled by setting the *PrtFrmEn* bit in the ITIMECONFIG register to a logic 0 or by programming 0.

## Functional Description (continued)

## 7.0 BLACK LEVEL & OFFSET ADJUSTMENT

The KAC-9637 allows for both fine and coarse black level adjustment. Coarse adjustment is made using the PIXELOFF-SET register and only needs to be done once at power up. Fine offset adjustment is done on a row basis and can be accomplished either atomically using the on chip black level compensation circuit or manually by disabling the on chip black level compensation circuit.

## 7.1 Coarse Black Level and Offset Adjustment

To ensure maximum performance of the CMOS image sensor, the natural offset of the pixel array needs to be minimized. Coarse adjustment is made using the PIXELOFFSET register and only needs to be done once at power up. This procedure is explained in detail in KAC-9637 Application Note 4.

## 7.2 Manual Black Level and Offset Adjustment

The offset channel can provide up to 255 levels of black level and offset adjustment. To manually adjust the black level and offset the *BlkLevEn* bit in the BLKLEVCONFIG register should be set to a logic 1. Eight bit offset values can then be programmed to register OFFSET.

Up to 255 levels of black level and offset adjustment are provided. To manually adjust the black level and offset the BlkLevEn bit in the BLKLEVCONFIG register should be set to a logic 0. The eight bit offset value can then be programmed using the Offset parameter in the OFFSET register.

## 7.3 Auto Black Level and Offset Adjustment

Automatic black level and offset adjustment mode is enabled by setting the *BlkLevEn* bit in the BLKLEVCONFIG register to a logic 0.

Figure 21: Digital Black Level & Offset Adjustment Loop

Figure 21 illustrates the automatic black level and offset compensation circuit contained within the sensor. For every row, the digitized values of the middle 8 black pixels are acquired and fed to the compensation level calculator circuit. This circuit is a digital first order exponential averaging filter. It calculates the compensation level (cmpl) that is required to ensure that for pixels that are optically black, the black level at the output of the ADC is equal to the desired black level. The desired black level (Clk-Target) can be programmed in the BLKTARGET register.

The black level control loop not only controls the black level of the pixels in the sensor array, but also controls the offset of the PGA and A/D in the system. The convergence rate of the cancellation loop can be set by programming the *BlkRate* parameter located in the BLKLEVCONFIG register. Small values of the *BlkRate* parameter ensure a fast convergence. High values of the *BlkRate* parameter reduce the noise in the calculated compensation level. The optimal setting of the *BlkRate* parameter is the result of a compromise between convergence speed after power up and image quality.

## 8.0 SYSTEM MANAGMENT

#### 8.1 System Reset

Upon power up an on-chip power on reset block will ensure that the sensor is initialized to its reset state. After power up the sensor can be reset by asserting a logic 0 on the **resetb** pin or by writing to the *SenReset* bin in the PWD&RESET register.

Furthermore, all state machines contained in the sensors integrated timing and control block can be reset by writing to the *RstzSoft* bit in the OPCTRL register.

## 8.2 Power Up and Down

The KAC-9637 is equipped with an on-board power management system allowing the analog and digital circuitry to be switched off (power down) and on (power up) at any time.

The sensor can be put into power down mode by asserting a logic one on the **pdwn** pin or by writing to the *PwDn* bit in the PWD&RST register.

To power up the sensor a logic zero can be asserted on the **pdwn** pin or by writing to the *PwDn* bit in the PWD&RST register.

To ensure proper sensor operation the reference ladders must be intitialized upon power up of the sensor.

To switch on the sensor's reference resistors, the following sequence of codes should be written to the sensor via the  ${\rm I}^2 C$  compatible interface at power up.

This must be done for the sensor to operate properly after reset or when the sensor is powered up.

| Address<br>(Hex) | Data<br>(Hex) |

|------------------|---------------|

| INITREG2         | 01            |

| POWCTRL          | 81            |

## **Functional Description**

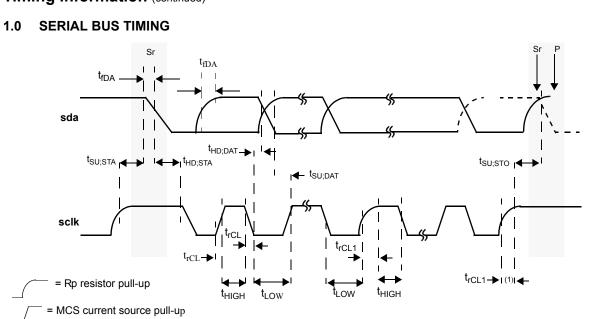

## 9.0 SERIAL BUS

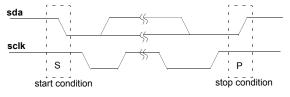

The serial bus interface consists of the  ${\bf sda}$  (serial data) and  ${\bf sclk}$  (serial clock) pins. The KAC-9637 can operate only as a slave.

The **sclk** pin is an input, it only controls the serial interface, all other clock functions within KAC-9637 use the master clock pin, **mclk**. **Mclk** must be running at least 4 times faster than **sclk** to write to the serial bus.

#### 9.1 Start/Stop Conditions

The serial bus will recognize a logic 1 to logic 0 transition on the **sda** pin while the **sclk** pin is at logic 1 as the **start** condition. A logic 0 to logic 1 transition on the **sda** pin while the **sclk** pin is at logic 1 is interrupted as the **stop** condition as shown in Figure 22.

Figure 22. Start/Stop Conditions

#### 9.2 Device Address

The *Device Address* can be changed by writing to the *l2cDevAddr* parameter in the *l2CMODE* Register.

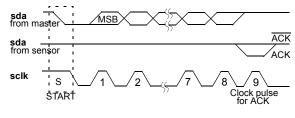

#### 9.3 Acknowledgment

The KAC-9637 will hold the value of the **sda** pin to a logic 0 during the logic 1 state of the *Acknowledge* clock pulse on **sclk** as shown in Figure 23.

#### 9.4 Data Valid

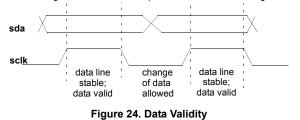

The master must ensure that data is stable during the logic 1 state of the **sclk** pin. All transitions on the **sda** pin can onlyoccur when the logic level on the sclk pin is "0" as shown in Figure 24

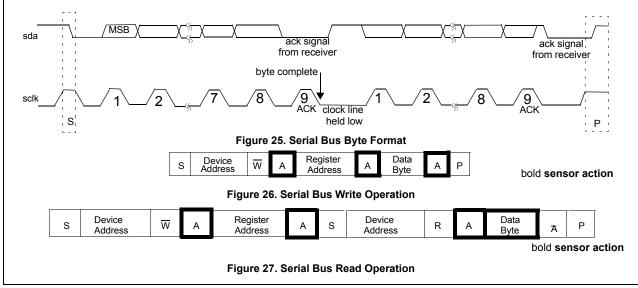

#### 9.5 Byte Format

Every byte consists of 8 bits. Each byte transferred on the bus must be followed by an *Acknowledge*. The most significant bit of the byte is should always be transmitted first. See Figure 25.

#### 9.6 Write Operation

A write operation is initiated by the master with a *Start Condition* followed by the sensor's *Device Address* and *Write* bit. When the master receives an *Acknowledge* from the sensor it can transmit an 8-bit internal register address. The sensor will respond with a second *Acknowledge* signaling the master to transmit 8 write data bits. A third *Acknowledge* is issued by the sensor when the data has been successfully received. The write operation is completed when the master asserts a *Stop Condition* or a second *Start Condition*. See Figure 26.

#### 9.7 Read Operation

A read operation is initiated by the master with a *Start Condition* followed by the sensor's *Device Address* and *Write* bit. When the master receives an *Acknowledge* from the sensor it can transmit the internal *Register Address* byte. The sensor will respond with a second *Acknowledge*. The master must then issue a new *Start Condition* followed by the sensor's *Device Address* and *read* bit. The sensor will respond with an Acknowledge followed by the *Read Data* byte.

The read operation is completed when the master asserts a *Not Acknowledge* followed by *Stop Condition* or a second *Start Condition*. See Figure 27.

#### 9.8 Advanced Write Mode

Several addresses can be written to without the need to re-start by setting the *AdvWr* bit in the I2CMODE register to a logic 1.

## Functional Description (continued)

#### **10.0 DIGITAL VIDEO PORT**

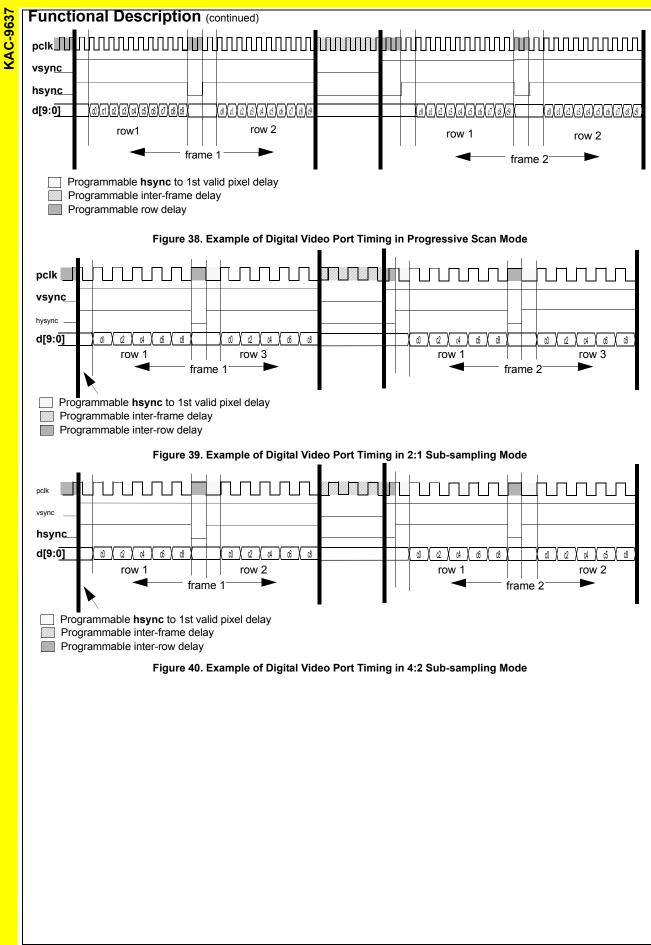

The captured image is placed onto a flexible 10-bit digital port as shown in Figure 9. The digital video port consists of a programmable 10-bit digital Data Out Bus (**d[9:0]**) and three programmable synchronisation signals (**hsync**, **vsync**, **pclk**).

By default the synchronisation signals are configured to operate in *"slave"* mode. They can be programmed to operate in *"master"* mode.

The following sections are a detailed description of the timing and programming modes of digital video port.

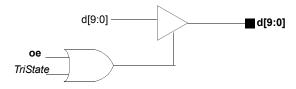

The 10-bit digital video out bus can be tri-stated by asserting a logic 0 on the **oe** pin or by writing a logic 1 to the *TriState* bit in the DVBUSCONFIG3 register. In addition to this, the 10-bit digital video bus can be switch off to a logic 0 by writing a logic 0 to the *VBuSEn* bit of the DVBUSCONFIG2 register (see figure 28).

Figure 28. Digital Pixel Data Out Bus Circuit Diagram

#### 10.1 Digital Video Data Out Bus (d[9:0])

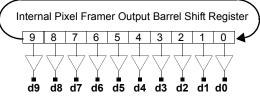

A programmable barrel shifter is provided to map the output of the internal pixel data framer to the pins of the digital video bus as illustrated in Figure 29.

Figure 29. Digital Video Bus Switching Modes

The *Bshift* parameter in the DVBUSCONFIG2 register can be used to program the number of bits that the digital pixel data is shifted by.

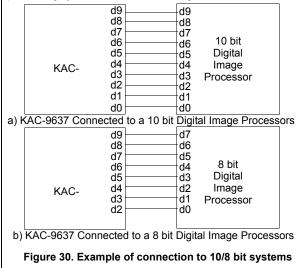

This feature allows a programmable digital gain to be implemented when connecting the sensor to 8 or 10 bit digital video processing systems as illustrated in Figure 30.

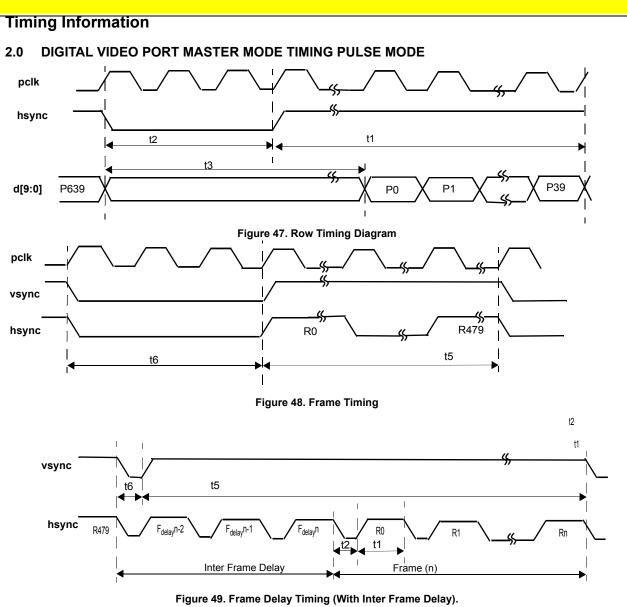

#### Synchronisation Signals in Master Mode

In master mode the integrated timing and control block controls the flow of data onto the 12-bit digital port, three synchronisation outputs are provided:

- pclk is the pixel clock output pin.

- **hsync** is the horizontal synchronisation output signal.

- **vsync** is the vertical synchronisation output signal.

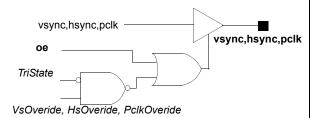

The vsync, hsync and pclk signals can be tri-stated by asserting a logic 0 on the oe pin or by writing a logic 0 to the *TriState* bit in the DVBUSCONFIG3 register. In addition to this vsync, hsync and pclk signals can be switch off by writing a logic 0 to the *VBuSEn* bit of the DVBUSCONFIG2 register. (see figure 31)

Figure 31. hsync,vsync and pclk output circuit diagram

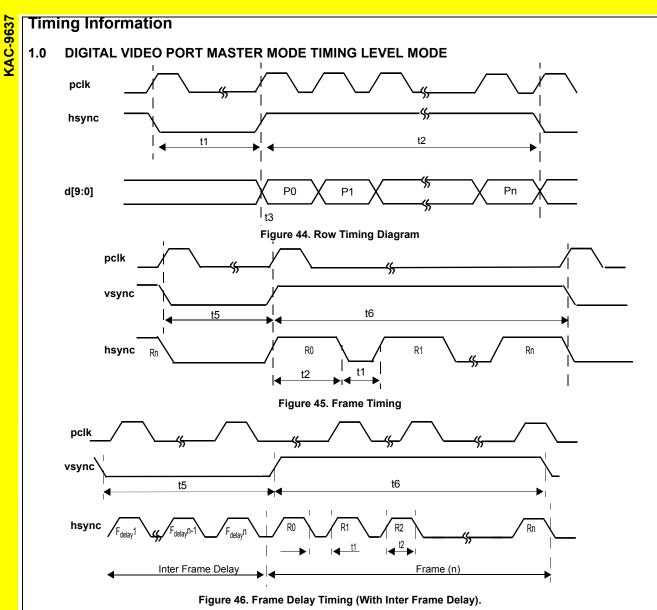

#### 10.2 Pixel Clock Output Pin (pclk) (Master Mode)

The pixel clock output pin, **pclk**, is provided to act as a synchronisation reference for the pixel data appearing at the digital video out bus pins **d[9:0]**. This pin can be programmed to operate in two modes:

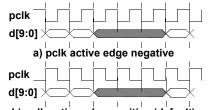

In free running mode, (the *PixClkMode* bit of DVBUSCONFIG1 register is set to a logic 0), the pixel clock output pin, **pclk**, is always running with a fixed period. Pixel data appearing on the digital video bus d[9:0] are synchronized to a specified active edge of the clock as shown in Figure 32.

b) pclk active edge positive (default) invalid pixel data

Figure 32. pclk in Free Running Mode

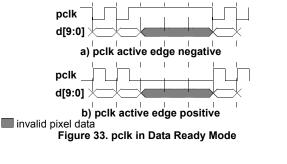

In data ready mode, (the PixClkMode bit of DVBUSCONFIG1 register is set to a logic 1), the pixel clock output pin pclk will produce a pulse with a specified level every time valid pixel data appears on the digital video bus d[9:0] as shown in Figure 33.

## Functional Description (continued)

By default the pixel clock is a free running active high (pixel data changes on the positive edge of the clock) with a period equal to the internal *hclk*. See section 6.3 for more **pclk** programming modes.

#### 10.3 Horizontal Synchronisation Output Pin (hsync)

The horizontal synchronisation output pin, **hsync**, is used as an indicator for row data. The **hsync** output pin can be programmed to operate in two modes as follows:

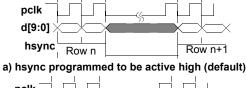

Level mode should be used when the pixel clock, pclk, is programmed to operate in *free running mode*. In level mode the hsync output pin will go to the specified level (high or low) at the start of each row and remain at that level until the last pixel of that row is read out on d[9:0] as shown in Figure 34. The hsync level is always synchronized to the active edge of pclk. The hsync pin is put into level mode by setting the *HsyncMode* bit of the DVBUSCONFIG1 register to a logic 0. The active level of the hsync pulse is programmed using the *HsyncPol* bit of the DVBUSCONFIG1 register.

Figure 34. hsync in Level Mode

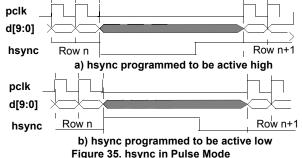

Pulse mode should be used when the pixel clock, pclk, is programmed to operate in *data ready mode*. In pulse mode the hsync output pin will produce a pulse at the end of each row. The width of the pulse will be a minimum of four pclk cycles and its polarity can be programmed as shown in Figure 35. The hsync level is always synchronized to the active edge of pclk. The hsync pin is put into pulse mode by setting the *HsyncMode* bit of the DVBUSCONFIG1 register to a logic 1.The active level of the hsync pulse is programmed using the HsyncPol bit of the DVBUSCONFIG1 register.

By default the first pixel data at the beginning of each row is placed on the digital video bus as soon as **hsync** is activated. Furthermore, **hsync** is de-activated upon the placement of the last pixel of the current row on the digital video bus the digital video bus. It is possible to shift the start and end edges of the **hsync** signal by programming the *HsyncStart* parameter of the DVBUSCONFIG0 register and the *HsyncEnd* parameter of the HYSNCADJUST register.

#### 10.4 Vertical/Horizontal Synchronisation Pin (vsync)

The vertical synchronisation output pin, **vsync**, is used as an indicator for pixel data within a frame. The **vsync** output pin can be programmed to operate in two modes as follows:

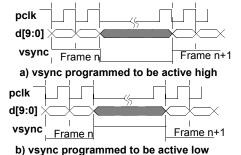

Level mode should be used when the pixel clock, pclk, is programmed to operate in *free running mode*. In level mode the vsync output pin will go to the specified level (high or low) at the start of each frame and remain at that level until the last pixel of that row in the frame is placed on d[9:0] as shown in Figure 36. The hsync level is always synchronized to the active edge of pclk. The vsync pin is put into level mode by setting the VsyncMode bit of the DVBUSCONFIG1 register to a logic 0. The active level of the DVBUSCONFIG1 register.

b) vsync programmed to be active lov

invalid pixel data

#### Figure 36. vsync in Level Mode

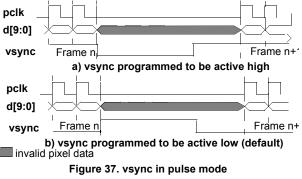

Pulse mode should be used when the pixel clock, pclk, is programmed to operate in *data ready mode*. In pulse mode the vsync output pin will produce a pulse at the end of each frame. The width of the pulse will be a minimum of four hclk cycles and its polarity can be programmed as shown in Figure 37. The vsync level is always synchronized to the active edge of pclk. The hsync pin is put into pulse mode by setting the *HsyncMode* bit of the DVBUSCONFIG1 register to a logic 1. The active level of the vsync pulse is programmed using the *VsyncPol* bit of the DVBUSCONFIG1 register.

By default the first pixel data at the beginning of each frame is placed on the digital video bus as soon as **vsync** is activated. Furthermore, **vsync** is de-activated upon the placement of the last pixel of the current frame on the digital video bus. It is possible to shift the start and end edges of the **vsync** signal by programming the *VsyncStart* parameter of the DVBUSCONFIG0 register and the *VsyncEnd* parameter of the HYSNCADJUST register.

#### **IMAGE SENSOR SOLUTIONS**

## Functional Description (continued)

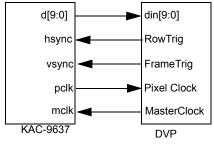

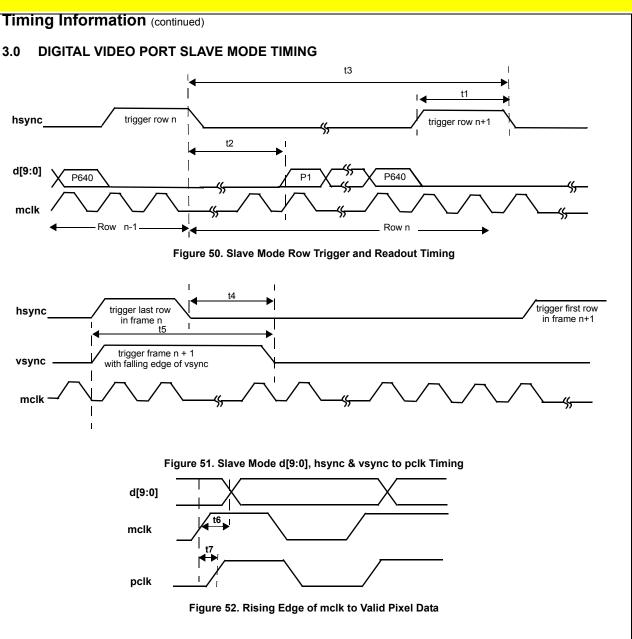

#### 10.5 Synchronisation Signals in Slave Mode

By default the sensor's digital video port synchronisation signals are configured to operate in slave mode. In slave mode the integrated timing and control block will only start frame and row processing upon the receipt of triggers from an external source.

Note:

1. Partial frame integration is disabled in slave mode.

In order to get all rows out of the device in slave mode VsynPol and HsynPol bits of register 0x53h must be set to 0

Only two synchronization signals are used in slave mode as follows:

hsync is the row trigger input signal. vsync is the frame trigger input signal.

Figure 41 shows the KAC-9637's digital video port in slave mode connected to a digital video processor master DVP.

#### Figure 41. KAC-9637 in slave mode

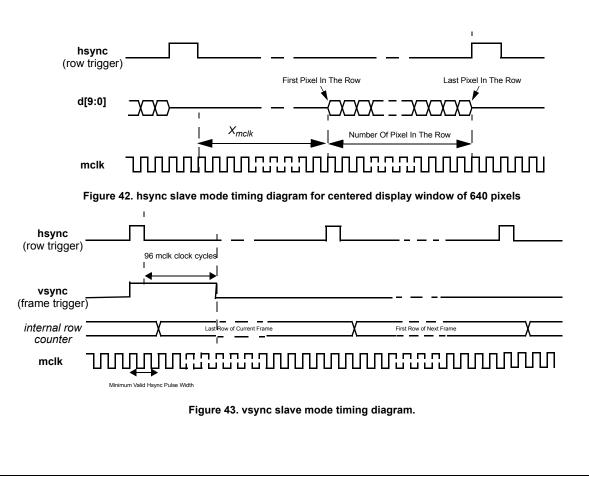

#### 10.6 Row Trigger Input Pin (hsync)

The row trigger input pin, **hsync**, is used to trigger the processing of a given row. It must be activated for at least two **mclk** cycles. The first pixel data will appear at **d[9:0]** " $X_{mclk}$ " periods after the falling edge of the row trigger, where  $X_{mclk}$  is given by:

X<sub>mclk</sub> = 146 + PrtFrmEn\*37 - 8\*BlkPixelEn

Where:

# *PrtFrmEn* is the partial frame integration bit setting in the ITIMECONFIG register.

BlkPixelEn

is the BlkPixelEn bit setting in the DVBUSCONFIG2 register

The polarity of the active level of the row trigger can be programmed using the HsynPol bit of the DVBUSCONFIG1 register. By default it is active high.

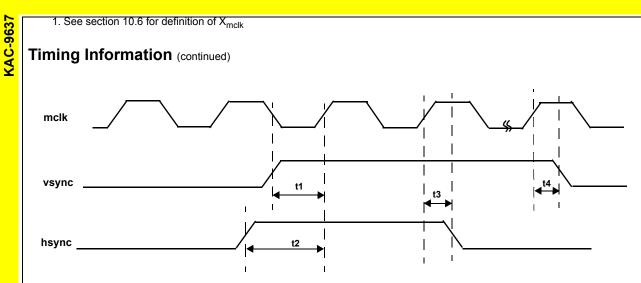

#### 10.7 Frame Trigger Input Pin (vsync)

The frame trigger input pin, **vsync**, is used to reset the row address counter and prepare the array for row processing. It must be activated for at least one more **mclk** cycle than the row trigger and the falling edge must be between 1 and 96 **mclk** cycles after falling edge of **hsync** as illustrated in Figure 43.

The polarity of the active level of the frame trigger is programmable. By default it is active high.

## MEMORY MAP

KAC-9637

| ADDR       | Register    | Reset Value    | Description                                                         |

|------------|-------------|----------------|---------------------------------------------------------------------|

| 00h        | DEVID       | 47h            | Device ID Register.                                                 |

| 01h        | REV         | Latest Silicon | Revision Register                                                   |

| 02h - 04h  |             |                | Reserved                                                            |

| 05h        | VCLKGEN     | 00h            | Clock Generation Register                                           |

| 06h        | PWD&RST     | 00h            | Power Down & Reset Register                                         |

| 07h        | I2CMODE     | AAh            | I <sup>2</sup> C compatible Serial Interface Configuration Register |

| 08h        |             |                | Reserved                                                            |

| 09h        | OPCTRL      | 02h            | Operation Control Register                                          |

| 0Ah - 0Fh  |             | 00h            | Reserved                                                            |

| 10h        | VIDCONFIG   | 01h            | Video Color Configuration Register                                  |

| 11h        | VSCAN       | 04h            | Vertical Scan Configuration Register                                |

| 12         |             |                | Reserved                                                            |

| 1 3h       | HSCAN       | 04h            | Horizontal Scan Configuration Register                              |

| 14h        |             |                | Reserved                                                            |

| 15h        | ITIMECONFIG | 08h            | Integration Time Configuration Register                             |

| 16h-18h    |             |                | Reserved                                                            |

| 19h        | WROWS       | 00h            | Active Window Row Start Register                                    |

| 1Ah        | WROWE       | 16h            | Active Window Row End Register                                      |

| 1Bh        | WROWLSB     | 23h            | Active Window Row LSB Register                                      |

| 1Ch        | WCOLS       | 00h            | Active Window Column End Register                                   |

| 1Dh        | WCOLE       | 28h            | Active Window Column Start Register                                 |

| 1Eh        | WCOLE       | 23h            | Active Window Column LSB Register                                   |

| 20h        | FDELAYH     | 00h            | Frame Delay High Register                                           |

| 21h        | FDELAYL     | 08h            | Frame Delay Low Register                                            |

| 22h        | RDELAYH     | 00h            | Row Delay High Register                                             |

| 23h        | RDELAYL     | 08h            | Row Delay Low Register                                              |

| 24h        | ITIMEH      | 00h            | Integration Time High Register                                      |

| 25h        | ITIMEL      | 00h            | Integration Time Low Register                                       |

| 26h - 3Fh  |             |                | Reserved                                                            |

| 40h        | BLKLEV      | 07h            | Black Level Compensation Register                                   |

| 41h        | BLKTARGET   | 10h            | Black Level Target Register                                         |

| 42h        | PGA         | 00h            | Programmable Gain Amplifier                                         |

| 43h - 45fh |             |                | Reserved For The LM9648. Must be set to 00 Hex                      |

| 46h        | OFFSET      | 00h            | Gain Offset Register                                                |

| 47h - 4Ah  |             |                | Reserved For the LM9648. Must be set to 00 Hex.                     |

| 4Bh- 4Fh   |             |                | Reserved                                                            |

## MEMORY MAP (continued)

| ADDR      | Register     | Reset Value | Description                                |

|-----------|--------------|-------------|--------------------------------------------|

| 50h       | VSYNCADUST   | 08h         | Vsync Adjust Register                      |

| 51h       | HSYNCADUST   | 08h         | Hsync Adjust Register                      |

| 52h       | DVBUSCONFIG0 | 00h         | Digital Video Bus Configuration Register 0 |

| 53h       | DVBUSCONFIG1 | 0Ch         | Digtal Video Bus Configuration Register 1  |

| 54h       | DVBUSCONFIG2 | F0h         | Digtal Video Bus Configuration Register 2  |

| 55h       | DVBUSCONFIG3 | 00h         | Digtal Video Bus Configuration Register 3  |

| 56h - 7Fh |              |             | Reserved                                   |

| 80h       | INITREG1     | 00h         | Sensor Initialization Register 1           |

| 81h - 82h |              |             | Reserved                                   |

| 83h       | PIXELOFFSET  | 1Eh         | Sensor's Pixel Offset Register             |

| 84h       |              |             | Reserved                                   |

| 85h       | POWCTRL      | 81h         | Sensor's Power Down Control Register       |

| 86h - 87h |              |             | Reserved                                   |

| 88h       | INITREG2     | 00h         | Sensor Initialization Register 2           |

## **Register Set**

KAC-9637

The following section describes all available registers in the KAC-9637 register bank and their function.

| Register I<br>Address<br>Mnemoni<br>Type<br>Reset Val                                                                                                                     | Read Onl   |                                                                                                                                                                                                                                                                          |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                                                                                                                                                                       | Bit Symbol | Description                                                                                                                                                                                                                                                              |  |  |

| 7:0                                                                                                                                                                       | Devld      | The sensor's device ID.                                                                                                                                                                                                                                                  |  |  |

| Register Name Silicon R<br>Address 01 Hex<br>Mnemonic REV<br>Type Read On<br>Reset Value Latest Si                                                                        |            |                                                                                                                                                                                                                                                                          |  |  |

| Bit                                                                                                                                                                       | Bit Symbol | Description                                                                                                                                                                                                                                                              |  |  |

| 7:0                                                                                                                                                                       | SiRev      | The sensor's silicon revision.                                                                                                                                                                                                                                           |  |  |

| Register Name     Clock Gen       Address     05 Hex       Mnemonic     VCLKGEN       Type     Read/Write       Reset Value     00 Hex.                                   |            | N                                                                                                                                                                                                                                                                        |  |  |

| Bit                                                                                                                                                                       | Bit Symbol | Description                                                                                                                                                                                                                                                              |  |  |

| 7                                                                                                                                                                         |            | Reserved.                                                                                                                                                                                                                                                                |  |  |

| 2:1                                                                                                                                                                       | HclkGen    | Use to divide the frequency of<br>the sensors master clock input,<br>mclk, and generate the sen-<br>sor's internal clock, <i>hclk</i> .<br>$\begin{array}{c cccc} 00 & \div 1(default) \\ \hline 01 & \div 2 \\ \hline 10 & \div 4 \\ \hline 11 & \div 6 \\ \end{array}$ |  |  |

| 0                                                                                                                                                                         |            | Reserved.                                                                                                                                                                                                                                                                |  |  |